#### University of New Mexico UNM Digital Repository

**Computer Science ETDs**

**Engineering ETDs**

7-1-2016

# Scheduling Heterogeneous HPC Applications in Next-Generation Exascale Systems

Oscar Hernan Mondragon Martinez

Follow this and additional works at: https://digitalrepository.unm.edu/cs\_etds

#### **Recommended** Citation

Mondragon Martinez, Oscar Hernan. "Scheduling Heterogeneous HPC Applications in Next-Generation Exascale Systems." (2016). https://digitalrepository.unm.edu/cs\_etds/78

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

### Oscar Hernán Mondragón Martínez

Candidate

### Computer Science

Department

This dissertation is approved, and it is acceptable in quality and form for publication:

Approved by the Dissertation Committee:

Patrick G. Bridges, Chairperson

Dorian Arnold

Trilce Estrada

Wei Wennie Shu

### Scheduling Heterogeneous HPC Applications in Next-Generation Exascale Systems

by

#### Oscar Hernán Mondragón Martínez

B.S., Electronics and Telecommunications Engineering, Universidad del Cauca, 2004

M.S., Wireless Systems and Related Technologies, Politecnico di Torino, 2006

M.S., Computer Science, University of New Mexico, 2013

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

July, 2016

©2016, Oscar Hernán Mondragón Martínez

# Dedication

To Leidy for her unconditional love, tireless support and unlimited patience; and to Emiliano, my inspiration and reason to keep fighting.

# Acknowledgments

During the time I was a graduate student in UNM and worked on my dissertation I received valuable feedback and help from numerous people. I would like to express my truly gratitude to all of them.

First, I would like to thank to my advisor, Patrick Bridges for his generosity and extremely useful guidance and support during all my time as a graduate student in UNM. Patrick truly believed in my work and devoted enormous amounts of time and effort sharing with me his knowledge and expertise in computer science and research matters. I am privileged to have worked with him and I feel sincerely grateful for all the help he provided to succesfully complete this work.

I wish to thank to Trilce Estrada, Dorian Arnold, and Wei Wennie Shu, who served as members of this dissertation committee, for their time and valuable suggestions to improve this work. I would like to express my thanks to Kevin Pedretti and Terry Jones who also contributed with feedback and good ideas during different stages of my dissertation. I would like to thank to Amanda Minnich who gave me precious feedback during my dissertation proposal elaboration. I wish to thank to Scott Levy, Kurt Ferreira, and Patrick Widener. I received valuable help and feedback while working with them and learnt a lot on doing quality research. I also want to thank to the members of the Scalable System Lab and the Hobbes project team who always provided good suggestions to improve my work.

I would like to acknowledge to Fulbright Colombia, Colciencias and the Universidad Autonoma de Occidente for the sponsorship they provided during my Ph.D. program, and to the 2013 Exascale Operating and Runtime Systems Program from the DOE Office of Science, Advanced Scientific Computing Research, which supported this work under the award number DE-SC0005050.

Finally, this work would have been imposible without the love and support of my family. I thank my wife, Leidy, and my son, Emiliano. They gave me the necessary encouragement and inspiration during all this process. I thank to my parents Omar and Elcy, for their love and support during this and all my projects; to my siblings Omar Arturo, Diana Karina, and Maria Eugenia; and to my nephews and niece Juan Sebastian, David, Felipe, and Sofia. They were always there for me.

### Scheduling Heterogeneous HPC Applications in Next-Generation Exascale Systems

by

#### Oscar Hernán Mondragón Martínez

B.S., Electronics and Telecommunications Engineering, Universidad del Cauca, 2004

M.S., Wireless Systems and Related Technologies, Politecnico di Torino, 2006

M.S., Computer Science, University of New Mexico, 2013

Ph.D., Computer Science, University of New Mexico, 2016

#### Abstract

Next generation HPC applications will increasingly time-share system resources with emerging workloads such as in-situ analytics, resilience tasks, runtime adaptation services and power management activities. HPC systems must carefully schedule these co-located codes in order to reduce their impact on application performance. Among the techniques traditionally used to mitigate the performance effects of timeshare systems is gang scheduling. This approach, however, leverages global synchronization and time agreement mechanisms that will become hard to support as systems increase in size. Alternative performance interference mitigation approaches must be explored for future HPC systems.

This dissertation evaluates the impacts of workload concurrency in future HPC systems. It uses simulation and modeling techniques to study the performance impacts of existing and emerging interference sources on a selection of HPC benchmarks, mini-applications, and applications. It also quantifies the cost and benefits of different approaches to scheduling co-located workloads, studies performance interference mitigation solutions based on gang scheduling, and examines their synchronization requirements.

To do so, this dissertation presents and leverages a new Extreme Value Theorybased model to characterize interference sources, and investigate their impact on Bulk Synchronous Parallel (BSP) applications. It demonstrates how this model can be used to analyze the interference attenuation effects of alternative fine-grained OS scheduling approaches based on periodic real time schedulers. This analysis can, in turn, guide the design of those mitigation techniques by providing tools to understand the tradeoffs of selecting scheduling parameters.

| List of Figures xiii |      |                                 |    |  |  |  |

|----------------------|------|---------------------------------|----|--|--|--|

| List of Tables       |      |                                 |    |  |  |  |

| 1                    | Intr | oduction                        |    |  |  |  |

|                      | 1.1  | Modern HPC architectures        | 4  |  |  |  |

|                      |      | 1.1.1 Composite Applications    | 4  |  |  |  |

|                      |      | 1.1.2 System Support Activities | 6  |  |  |  |

|                      | 1.2  | The Effects of Interference     | 8  |  |  |  |

|                      | 1.3  | Example                         | 9  |  |  |  |

|                      | 1.4  | Mitigating Interference Impacts | 10 |  |  |  |

|                      | 1.5  | Research Challenges             | 11 |  |  |  |

|                      | 1.6  | Contributions                   | 12 |  |  |  |

|                      | 1.7  | Dissertation Outline            | 13 |  |  |  |

#### 2 Related Work

15

|   | 2.1 | 1 Application Composition |                                                      |    |

|---|-----|---------------------------|------------------------------------------------------|----|

|   |     | 2.1.1                     | Example Composite Codes                              | 16 |

|   |     | 2.1.2                     | System Software Support for Analytics                | 17 |

|   |     | 2.1.3                     | Scheduling Analytics                                 | 18 |

|   | 2.2 | Perfor                    | mance Interference                                   | 19 |

|   |     | 2.2.1                     | Performance Interference Characterization            | 20 |

|   |     | 2.2.2                     | Summary                                              | 20 |

|   |     | 2.2.3                     | Simulating Interference Performance Impact           | 21 |

|   | 2.3 | Model                     | ing Performance Impact                               | 23 |

|   |     | 2.3.1                     | Modeling Extremes                                    | 23 |

|   |     | 2.3.2                     | Other Analytical Models                              | 27 |

|   | 2.4 | Perfor                    | mance Impact Mitigation                              | 28 |

|   |     | 2.4.1                     | Gang Scheduling                                      | 28 |

|   |     | 2.4.2                     | Real Time Scheduling Mitigation                      | 29 |

|   | 2.5 | Summ                      | ary                                                  | 31 |

| 3 | Cha | racter                    | izing Performance Impact                             | 34 |

|   | 3.1 | Introd                    | uction                                               | 34 |

|   | 3.2 | Evalua                    | ating Application/Analytics Performance Interactions | 36 |

|   |     | 3.2.1                     | Quantifying Analytics Scheduling Impacts             | 36 |

|   |     | 3.2.2                     | Simulating Time-sharing                              | 37 |

|   |     | 3.2.3  | Application Workload Details              | 38 |

|---|-----|--------|-------------------------------------------|----|

|   | 3.3 | Perfor | mance Interference Characterization       | 39 |

|   |     | 3.3.1  | Noise Characterization                    | 39 |

|   |     | 3.3.2  | Noise Performance Impact                  | 40 |

|   | 3.4 | Synch  | ronization Mechanisms                     | 45 |

|   |     | 3.4.1  | System-based Synchronization Services     | 45 |

|   |     | 3.4.2  | Synchronizing Collective Operations       | 46 |

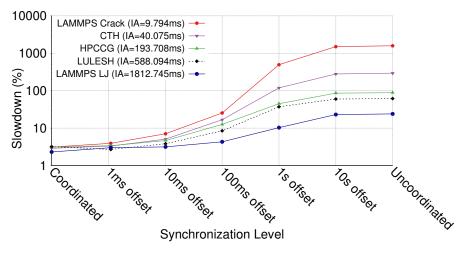

|   | 3.5 | Synch  | ronization Requirements                   | 46 |

|   | 3.6 | Analy  | sis and Discussion of Results             | 48 |

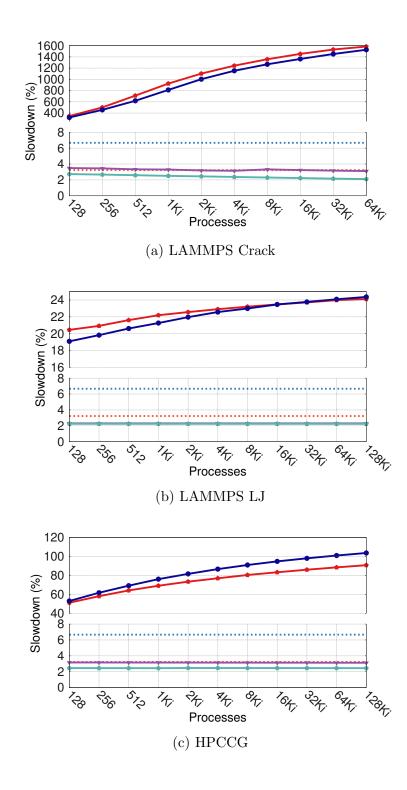

|   |     | 3.6.1  | Time-sharing vs. Space-sharing            | 48 |

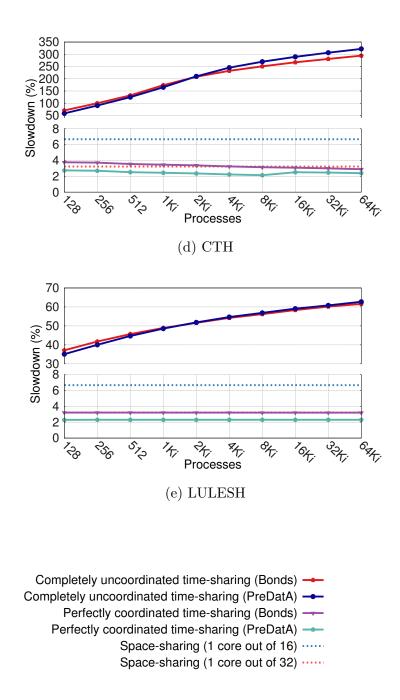

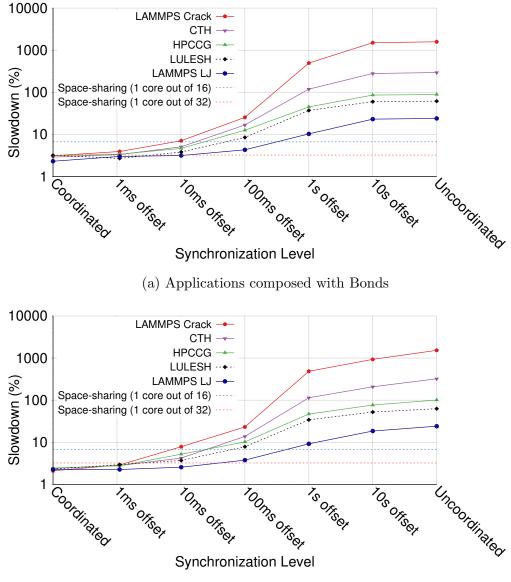

|   |     | 3.6.2  | Variations in Application Response        | 49 |

|   |     | 3.6.3  | Effectiveness of Gang Scheduling          | 49 |

|   | 3.7 | Summ   | ary                                       | 51 |

| 4 | Mo  | deling | HPC Application Interference              | 53 |

|   | 4.1 | Introd | uction                                    | 53 |

|   | 4.2 | Model  | ing HPC Performance Interference          | 54 |

|   |     | 4.2.1  | Modeling Approach                         | 55 |

|   |     | 4.2.2  | Estimating Model Parameters               | 56 |

|   |     | 4.2.3  | Choosing Block Sizes and Number of Blocks | 57 |

|   |     | 4.2.4  | Extrapolating Model Performance           | 59 |

|   | 4.3                      | Model                                                 | Validation                                                   | 59                                                                                             |

|---|--------------------------|-------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   |                          | 4.3.1                                                 | Validation Framework                                         | 60                                                                                             |

|   |                          | 4.3.2                                                 | Validation Against Varying Local Computation Distributions . | 62                                                                                             |

|   |                          | 4.3.3                                                 | Validation Against Varying Interference Sources              | 64                                                                                             |

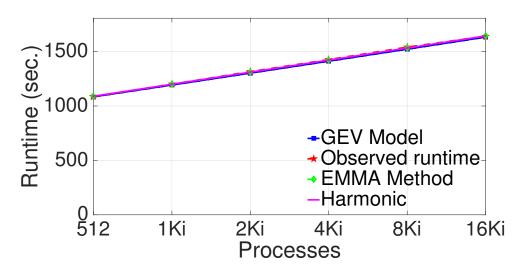

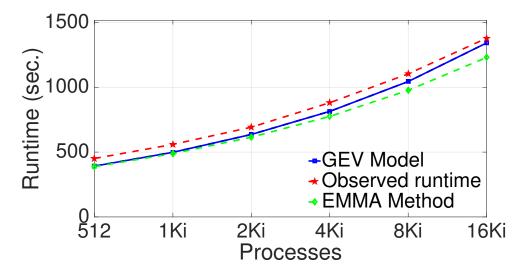

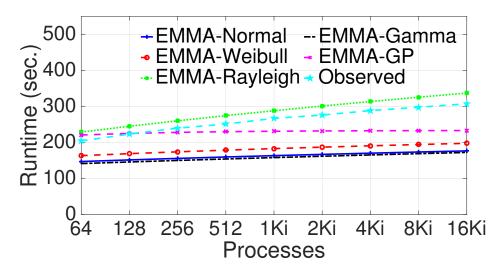

|   |                          | 4.3.4                                                 | Noise Performance Impact Comparison vs. EMMA Method          | 66                                                                                             |

|   | 4.4                      | Interfe                                               | rence Workload Characterization                              | 70                                                                                             |

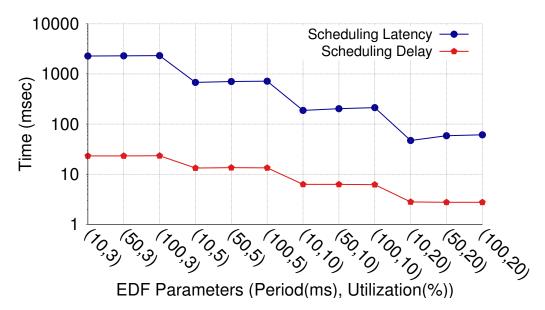

|   | 4.5                      | Predic                                                | ting Application Performance Impact                          | 71                                                                                             |

|   |                          | 4.5.1                                                 | Evaluation Methodology                                       | 71                                                                                             |

|   |                          | 4.5.2                                                 | OS Noise and Analytics Interference                          | 73                                                                                             |

|   |                          | 4.5.3                                                 | Asynchronous Checkpointing Interference                      | 73                                                                                             |

|   |                          |                                                       |                                                              |                                                                                                |

|   | 4.6                      | Summ                                                  | ary                                                          | 79                                                                                             |

| 5 |                          |                                                       | ary                                                          | 79<br><b>80</b>                                                                                |

| 5 |                          | lerstan                                               |                                                              |                                                                                                |

| 5 | Und                      | <b>lerstan</b><br>Introd                              | ding Performance Impact Mitigation Strategies                | 80                                                                                             |

| 5 | <b>Und</b><br>5.1        | <b>lerstan</b><br>Introd                              | ding Performance Impact Mitigation Strategies                | <b>80</b><br>80<br>81                                                                          |

| 5 | <b>Und</b><br>5.1        | lerstan<br>Introd<br>EDF-b                            | ding Performance Impact Mitigation Strategies         uction | <b>80</b><br>80<br>81                                                                          |

| 5 | <b>Und</b><br>5.1        | lerstan<br>Introd<br>EDF-b<br>5.2.1                   | ding Performance Impact Mitigation Strategies         uction | <ul> <li>80</li> <li>80</li> <li>81</li> <li>81</li> </ul>                                     |

| 5 | <b>Und</b><br>5.1        | lerstan<br>Introd<br>EDF-b<br>5.2.1<br>5.2.2<br>5.2.3 | ding Performance Impact Mitigation Strategies         uction | <ul> <li>80</li> <li>80</li> <li>81</li> <li>81</li> <li>84</li> </ul>                         |

| 5 | <b>Und</b><br>5.1<br>5.2 | lerstan<br>Introd<br>EDF-b<br>5.2.1<br>5.2.2<br>5.2.3 | ding Performance Impact Mitigation Strategies         uction | <ul> <li>80</li> <li>80</li> <li>81</li> <li>81</li> <li>84</li> <li>85</li> <li>86</li> </ul> |

|              | 5.4                                                                 | Summ    | ary                                                             | 101 |

|--------------|---------------------------------------------------------------------|---------|-----------------------------------------------------------------|-----|

| 6            | Con                                                                 | clusio  | n & Future Work                                                 | 102 |

|              | 6.1                                                                 | Summ    | ary                                                             | 102 |

|              | 6.2                                                                 | Future  | e Work                                                          | 104 |

|              |                                                                     | 6.2.1   | Characterizing Dynamic Hardware Impacts                         | 104 |

|              |                                                                     | 6.2.2   | Investigating Emerging Programming Models                       | 104 |

|              |                                                                     | 6.2.3   | Studying Interference Sources with Large Block Size Require-    |     |

|              |                                                                     |         | ments                                                           | 105 |

|              |                                                                     | 6.2.4   | Investigating Communicating Analytics workloads                 | 105 |

| Aj           | ppen                                                                | dices   |                                                                 | 106 |

| $\mathbf{A}$ | Pre                                                                 | dicting | g Interference Performance Impact                               | 107 |

|              | A.1 Interference Performance Impact Prediction on the Synthetic BSP |         |                                                                 |     |

|              |                                                                     | Bench   | mark                                                            | 107 |

|              | A.2                                                                 | Interfe | erence Performance Impact Prediction on Applications $\ldots$ . | 110 |

|              | A.3                                                                 | EDF-S   | Scheduled Workloads Performance Impact Prediction               | 113 |

| Re           | efere                                                               | nces    |                                                                 | 115 |

# List of Figures

| 1.1 | Resource allocation options                                                                                                                          | 3  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | In situ analytics application                                                                                                                        | 5  |

| 2.1 | System software support for <i>in situ</i> analytics                                                                                                 | 18 |

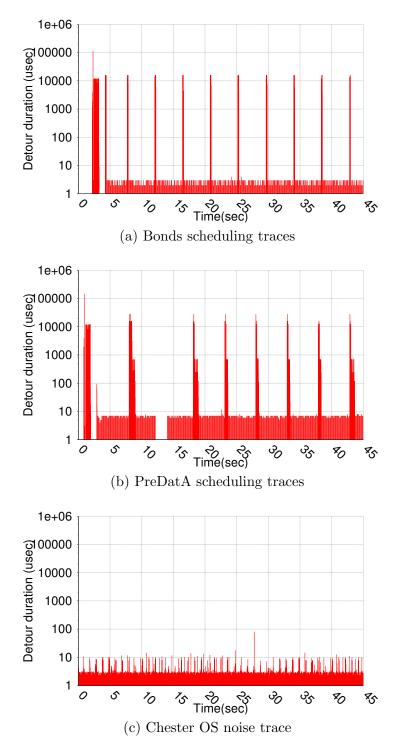

| 3.1 | $In\ situ$ analytics scheduling traces and Chester OS noise profile                                                                                  | 42 |

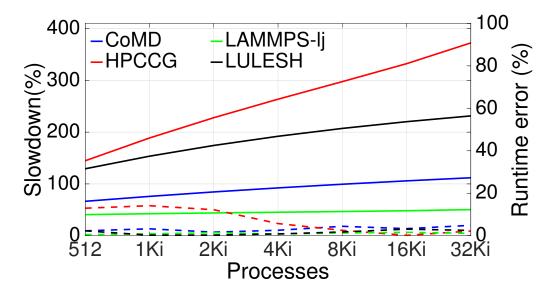

| 3.2 | Impact of $in\ situ$ analytics codes on applications' performance $\ldots$                                                                           | 44 |

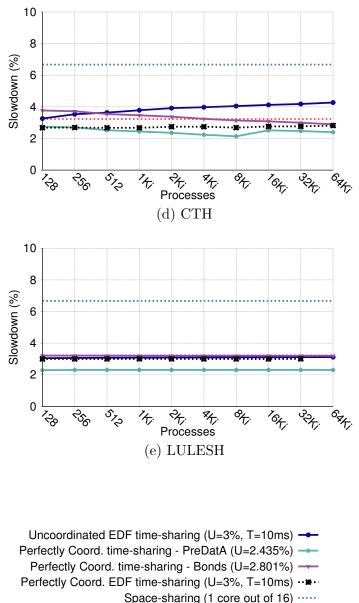

| 3.3 | Effect of coordinated scheduling synchronization on applications' per-<br>formance                                                                   | 47 |

| 3.4 | Statistical distribution of inter-arrival times for a set of applications                                                                            | 50 |

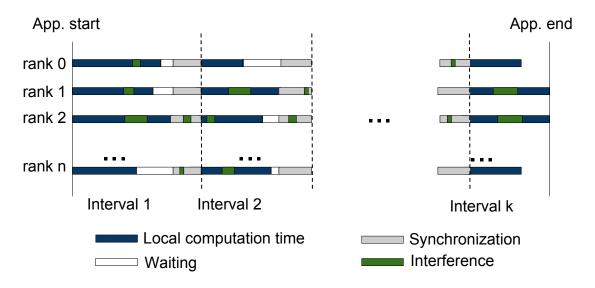

| 4.1 | BSP Application affected by interference                                                                                                             | 55 |

| 4.2 | Synthetic test pseudo-code                                                                                                                           | 60 |

| 4.3 | Runtime estimates for the synthetic application with local computa-<br>tion times exponentially distributed with mean = $160 \text{ ms} \dots \dots$ | 64 |

| 4.4 | Runtime estimates for the synthetic benchmark with Pareto-distributed local computation times (Pareto shape $(\alpha) = 3$ , scale = 40 ms)          | 65 |

| 4. | 5  | GEV model performance impact predictions for the synthetic BSP test-case                                                                               | 68 |

|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4. | 6  | Performance impact prediction for the BSP synthetic application in<br>the presence of interference using EMMA EMV method                               | 69 |

| 4. | 7  | Noise profiling of different interference sources using the GEV model                                                                                  | 71 |

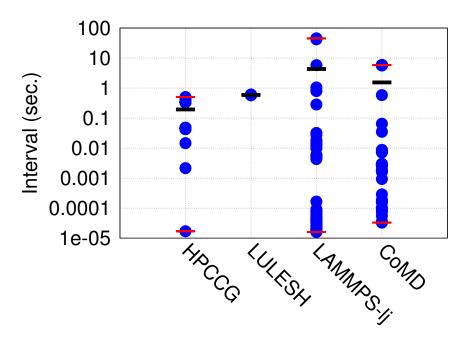

| 4. | 8  | Measured intervals between synchronizing MPI collective operations<br>for four applications.                                                           | 72 |

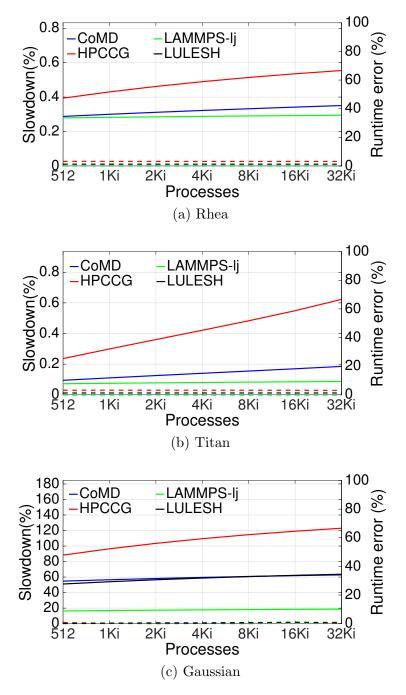

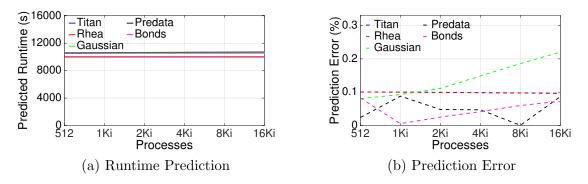

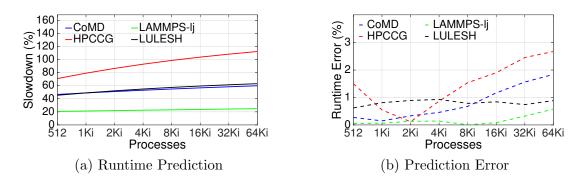

| 4. | 9  | Impact estimation using the GEV model of OS noise interference sources on a set of applications                                                        | 75 |

| 4. | 10 | Impact estimation using the GEV model of two <i>in situ</i> analytics on a set of applications                                                         | 76 |

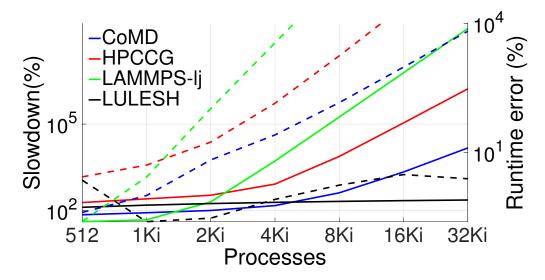

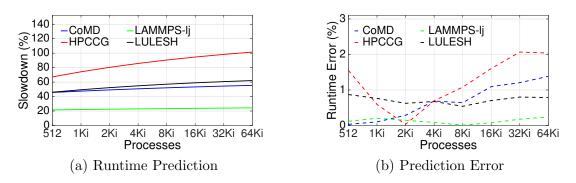

| 4. | 11 | Estimation using the GEV model of an asynchronous checkpointing task                                                                                   | 77 |

| 4. | 12 | Preliminary results estimating the impact of asynchronous check-<br>pointing on application performance using a hybrid model                           | 78 |

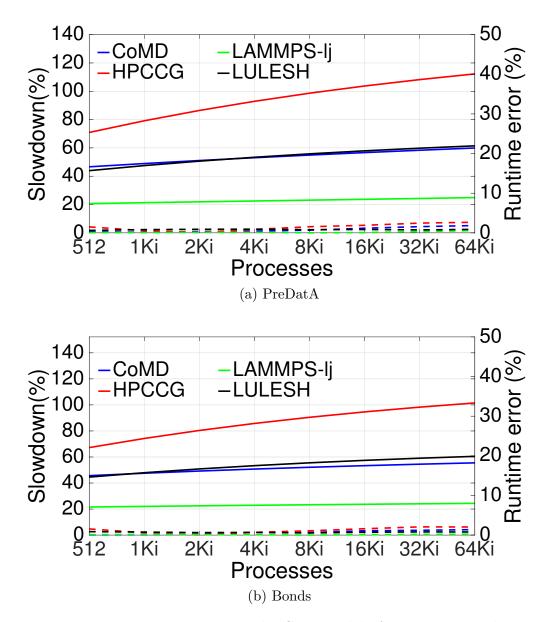

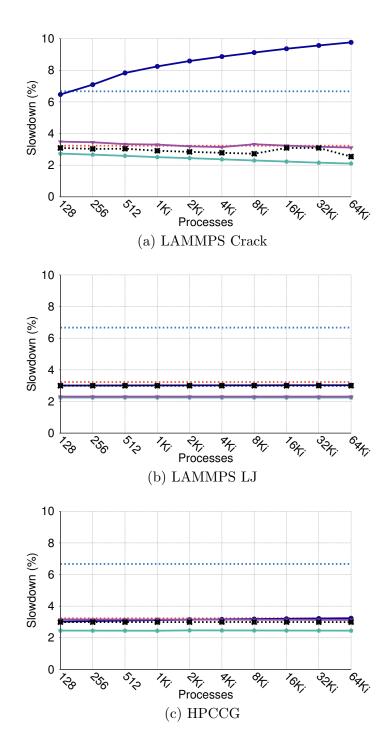

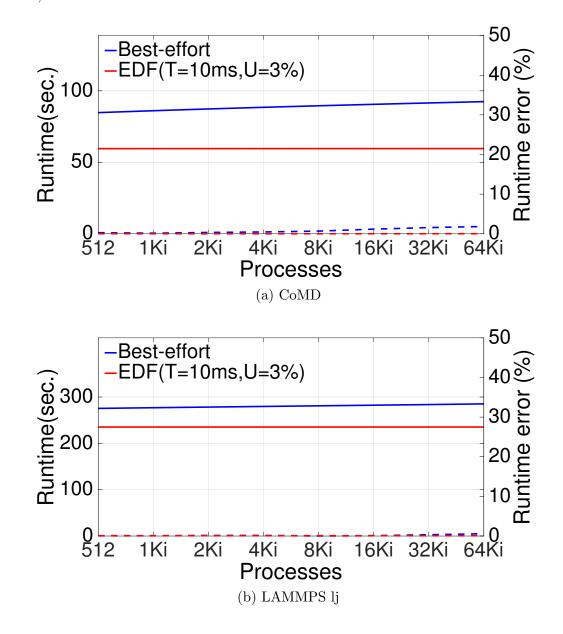

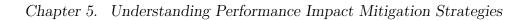

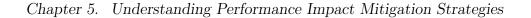

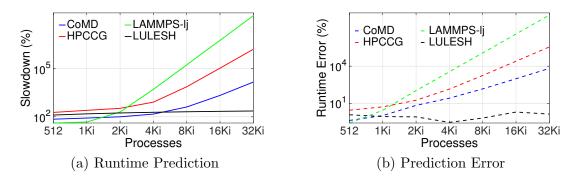

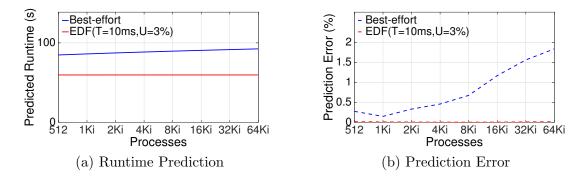

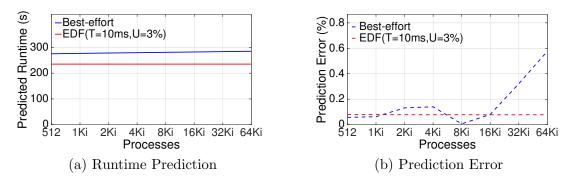

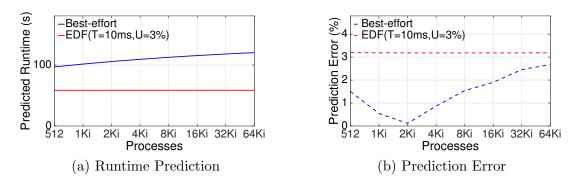

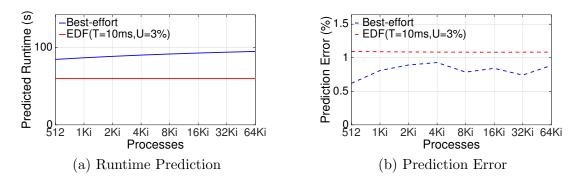

| 5. | 1  | Performance impact of EDF-scheduled analytics with EDF period 10 ms and utilization factor $3\%$                                                       | 83 |

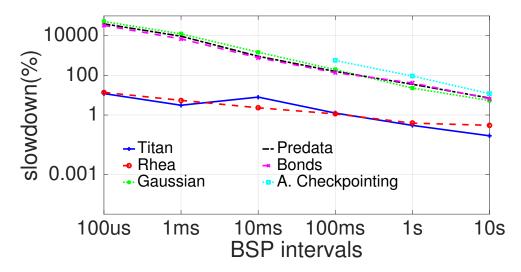

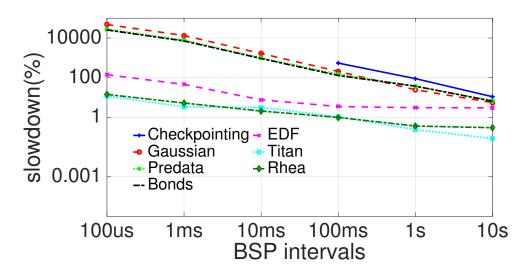

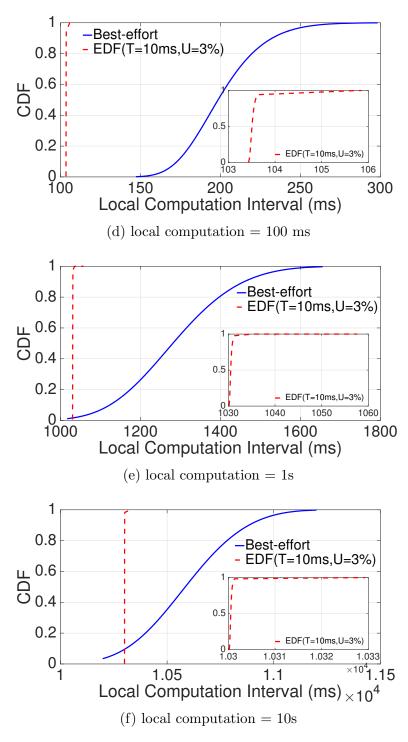

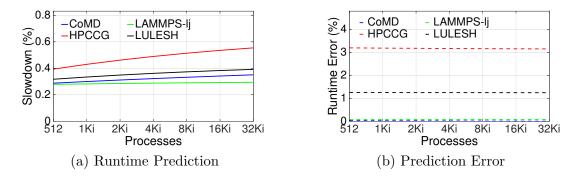

| 5. | 2  | Slowdowns for applications co-located with an EDF-scheduled workload                                                                                   | 85 |

| 5. | 3  | EDF $(T_i = 10 \text{ ms}, u_i = 3\%)$ scheduling mitigation effect on the synthetic BSP test-case for a range of interval lengths at 16,384 processes | 87 |

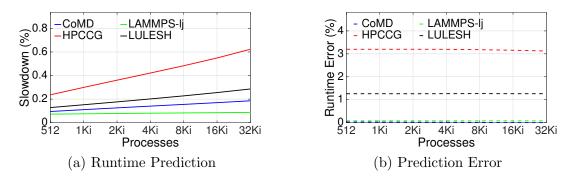

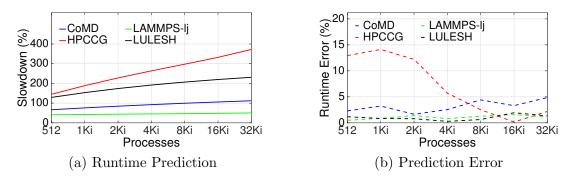

| 5. | 4  | Impact estimation using the GEV model of PreDatA on a set of applications using EDF and best-effort scheduling policies                                | 89 |

#### List of Figures

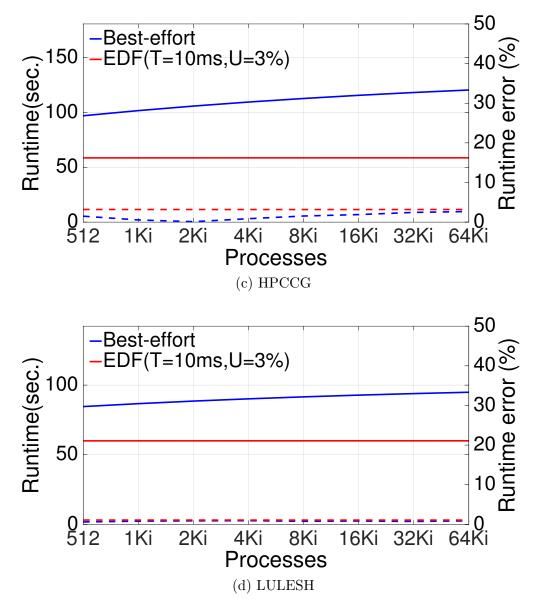

| 5.5 | CDFs for different values of BSP intervals under PreDatA interfer-                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

|     | ence for a 512 nodes count $\dots \dots 96$ |

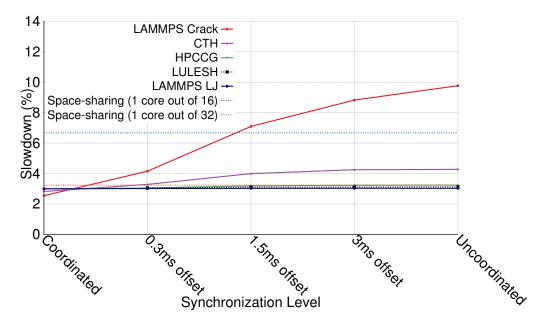

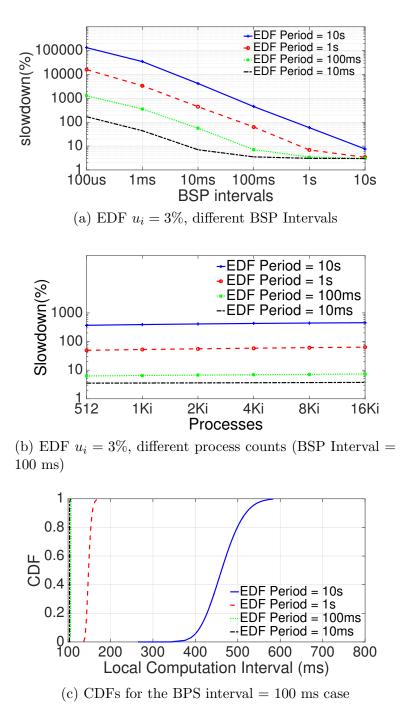

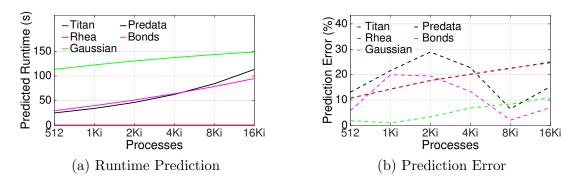

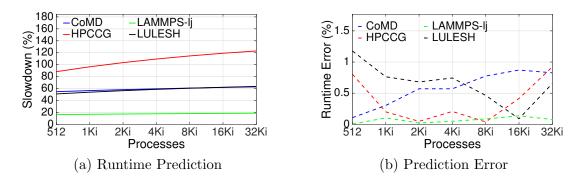

| 5.6 | Impact of EDF-scheduled workloads with different EDF periods $97$                                                               |

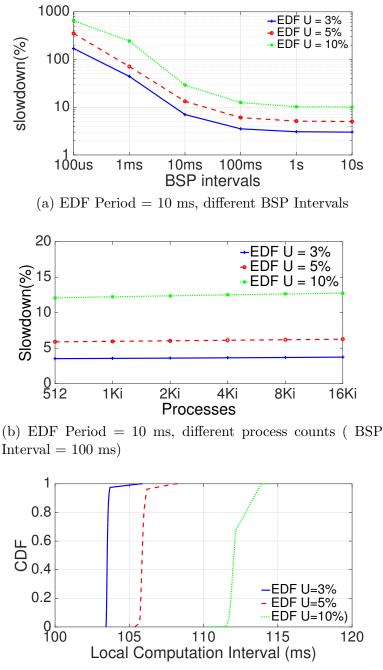

| 5.7 | Impact of EDF-scheduled workloads with different utilization factors 98                                                         |

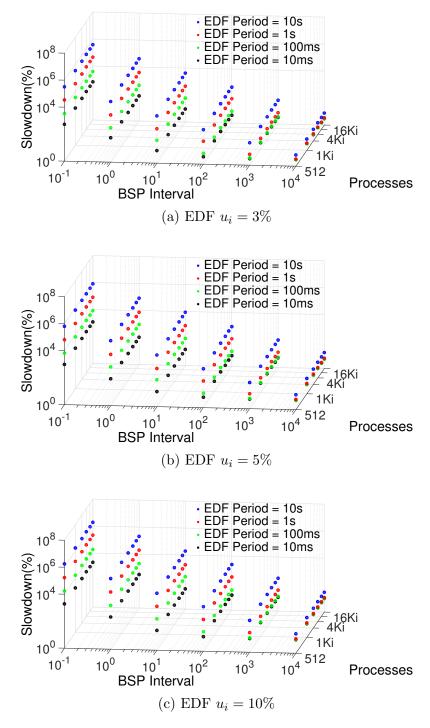

| 5.8 | EDF parameters tradeoffs for different utilization factors 99                                                                   |

| 5.9 | Scheduling delay and scheduling latency for different EDF Parameters100                                                         |

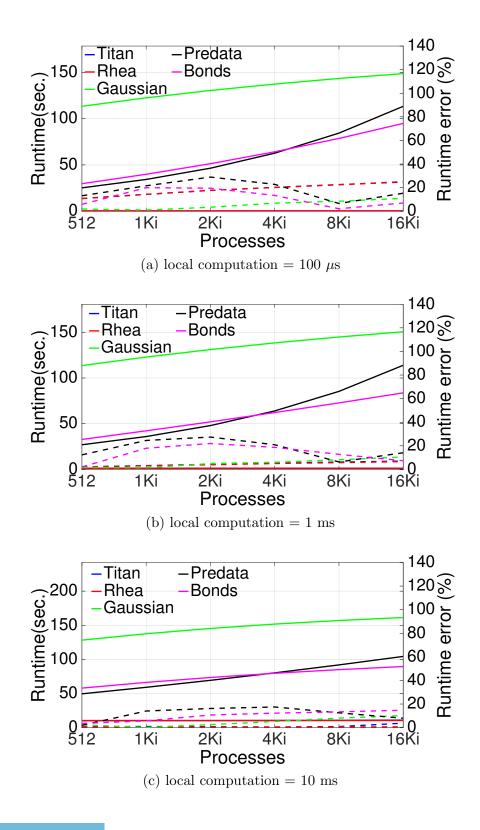

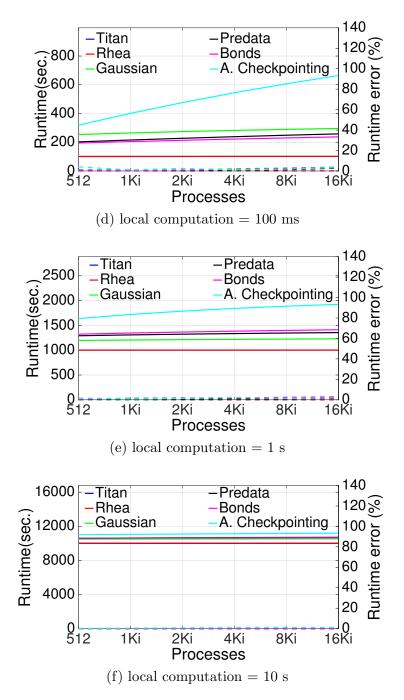

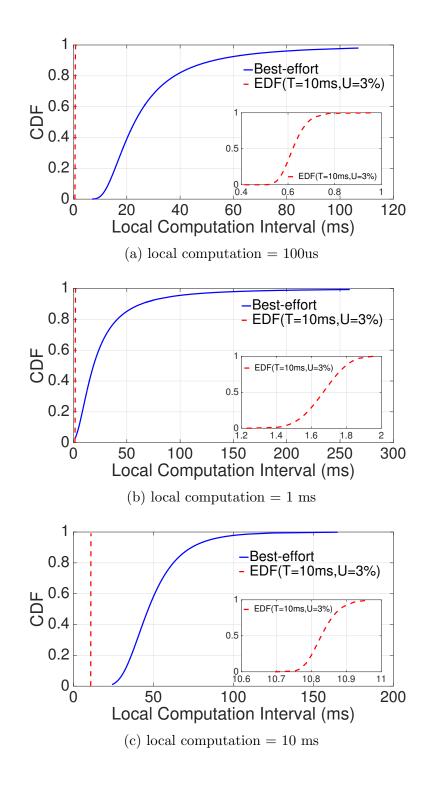

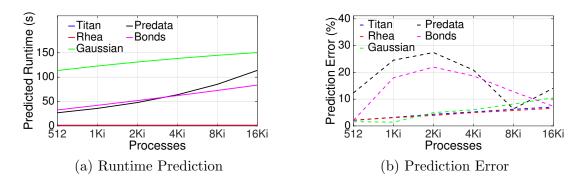

| A.1 | GEV model prediction of the performance impact of interference                                                                  |

|     | sources on the BSP synthetic benchmark with local computation of                                                                |

|     | $100 \ \mu s.$                                                                                                                  |

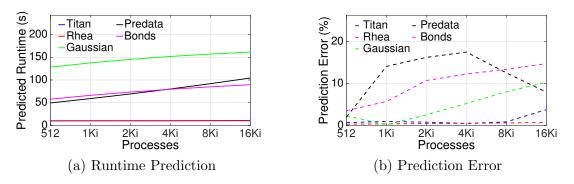

| A.2 | GEV model prediction of the performance impact of interference                                                                  |

|     | sources on the BSP synthetic benchmark with local computation of                                                                |

|     | 1 ms                                                                                                                            |

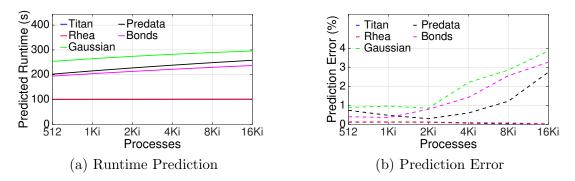

| A.3 | GEV model prediction of the performance impact of interference                                                                  |

|     | sources on the BSP synthetic benchmark with local computation of                                                                |

|     | 10 ms                                                                                                                           |

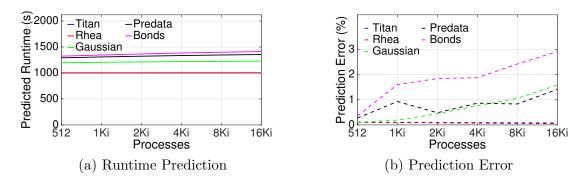

| A.4 | GEV model prediction of the performance impact of interference                                                                  |

|     | sources on the BSP synthetic benchmark with local computation of                                                                |

|     | 100 ms                                                                                                                          |

| A.5 | GEV model prediction of the performance impact of interference                                                                  |

|     | sources on the BSP synthetic benchmark with local computation of                                                                |

|     | 1 s                                                                                                                             |

| A.6 | GEV model prediction of the performance impact of interference<br>sources on the BSP synthetic benchmark with local computation of<br>10 s |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| A.7 | Rhea OS noise performance impact on applications predictions using<br>the GEV model                                                        |

| A.8 | Titan OS noise performance impact on applications predictions using<br>the GEV model                                                       |

| A.9 | Synthetic gaussian noise performance impact on applications predic-<br>tions using the GEV model                                           |

| A.1 | 0 PreDatA performance impact on applications predictions using the GEV model                                                               |

| A.1 | 1 Bonds performance impact on applications predictions using the GEV<br>model                                                              |

| A.1 | 2 Asynchronous checkpointing performance impact on applications pre-<br>dictions using the direct GEV model                                |

| A.1 | 3 Asynchronous checkpointing performance impact on applications pre-<br>dictions using the hybrid GEV model                                |

| A.1 | 4 PreDatA performance impact on CoMD prediction using the GEV<br>model. Best effort and EDF scheduling are compared                        |

| A.1 | 5 PreDatA performance impact on LAMMPS-lj prediction using the<br>GEV model. Best effort and EDF scheduling are compared 113               |

| A.1 | 6 PreDatA performance impact on HPCCG prediction using the GEV<br>model. Best effort and EDF scheduling are compared                       |

List of Figures

# List of Tables

| 3.1 | In situ analytics codes and OS noise traces statistics $\ldots$ $\ldots$ $\ldots$                                                                                                                                           | 40 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Estimated GEV parameters for the exponential distribution experi-<br>ments                                                                                                                                                  | 63 |

| 4.2 | Estimated GEV parameters for the pareto distribution experiments .                                                                                                                                                          | 63 |

| 5.1 | Estimated GEV parameters for PreDatA using best-effort and EDF $(T_i = 10 \text{ ms}, u_i = 3\%)$ scheduling for the synthetic benchmark with BSP intervals between 100 $\mu$ s and 10 s for a 512 nodes count (base case). | 91 |

| 5.2 | Estimated GEV parameters for EDF scheduled analytics for different<br>EDF periods and $u_i = 3\%$ for the synthetic benchmark with BSP<br>intervals of 100 ms                                                               | 92 |

| 5.3 | Estimated GEV parameters for EDF scheduled analytics for different<br>EDF utilization factors and an EDF period of 10 ms for the synthetic<br>benchmark with BSP intervals of 100 ms                                        | 93 |

# Chapter 1

# Introduction

Modern HPC (High Performance Computing) applications are used to solve advanced scientific problems in areas such as engineering, climate modeling, physics, and molecular dynamics. Those computational science programs generate large amounts of data that have to be prepared and analyzed before being presented to the field expert, who will use the resulting information to understand problems and inform decision making. To efficiently perform this, applications are increasingly coupled with analytics codes. This allows the system to periodically analyze data as it becomes available during application runtime.

These applications run in complex systems with limited resources that have to be shared with other applications and with system management activities. Next generation systems will face new challenges given this growing concurrency of workloads [4, 21, 54]. In addition to the mutual interference that may exist between co-existing codes, applications will have to deal with other interference sources such as background system tasks, resilience routines, runtime adaptation services, and power management policies. The random nature of the disruption events generated by those workloads causes significant variability in the performance of individual

parallel components affecting the overall application performance [21].

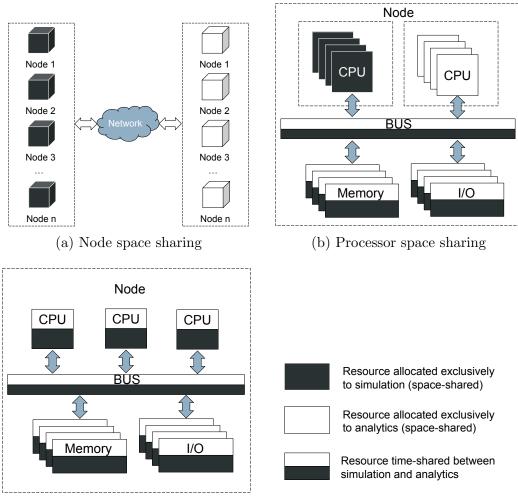

In order to optimize the performance of applications, the system software must make effective resource allocation decisions. In current HPC systems, resource allocation is based on coarse-grained *space-shared* policies, where workloads have exclusive access to a set of nodes while they are running. In this scheme, applications frequently use a subset of the compute nodes to run analytics. This requires expensive data movement between simulation and analytics nodes (as shown in Figure 1.1a).

These costs are motivating the use of alternative resource allocation policies where simulation is co-located on a node with analytics. This co-location of workloads can be done using fine grained space-sharing where applications and analytics run on a non-overlapping set of processors inside the node (as shown in Figure 1.1b) or using time-shared allocation policies where processors are shared (as shown in Figure 1.1c) by the coupled workloads. The advantage of time-sharing processors is that analytics can leverage idle processors times to run, using resources that otherwise are wasted [90].

Although moving from node space-sharing to workload co-location policies reduces data movement costs and uses processors more efficiently, the effects of noise and contention for resources can increase significantly [54]. Under the co-location scheme, separate application components contend for system resources such as memory last level caches, DRAM bandwidth, and device drivers. When using time-sharing policies CPU cores are also shared (see Figure 1.1). Additionally, the services required to support a given workload may result in OS activities (sometimes referred to as OS noise) that slow down coupled workloads.

Among the techniques to mitigate performance interference are hybrid spacesharing and time-sharing approaches [2], cooperative time-sharing [90], and gang scheduling [26]. This last approach, for example, concurrently schedules the parallel

(c) Time sharing

Figure 1.1: Resource allocation options

components of a workload across system partitions, facilitating those components making progress in parallel and avoiding the long blocking periods that occur if they are not scheduled at the same time. This technique leverages global synchronization and time agreement mechanisms, however, that are difficult to scale. Given this, alternative performance interference mitigation approaches must be explored for future HPC systems.

This dissertation evaluates the impacts of workload concurrency in future HPC systems. It studies current interference mitigation solutions based on gang scheduling and examines their synchronization requirements. This work also analyzes the interference attenuation effects of alternative fine-grained OS scheduling approaches based on periodic real time schedulers, providing the theoretical foundations to understand their impact on applications performance.

### 1.1 Modern HPC architectures

Modern HPC applications and systems are undergoing important changes. Largescale scientific applications are beginning to perform simulation and analysis concurrently instead of sequentially. Similarly, hardware memory and network bandwidth restrictions and system power caps also motivate the need to minimize data movement and power down unneeded hardware components whenever possible.

Under this scheme, system resources have to be shared between simulation and analytics workloads. Additionally, system tasks and other emerging workloads also compete for resources. In addition to the OS short-lived system tasks, which have been traditionally identified as interference sources, next-generation HPC applications will face new sources of contention such as resilience routines, and power management tasks. This section describes a set of workloads and architectures of these systems.

#### 1.1.1 Composite Applications

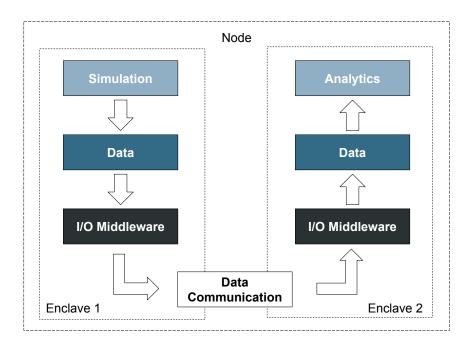

Modern HPC applications are complex and are composed of coupled individual workloads which are each comprised of several interacting components. Figure 1.2 shows an example of the components of simulation and analytics in an *in situ* analytics

application. Each portion of the applications runs in its own *enclave*, a set of system resources allocated to an application [4]. In Figure 1.2, enclave 1 contains the simulation code and enclave 2 holds the analytics code, and these enclaves are co-located on the same node.

Figure 1.2: In situ analytics application

#### Simulation

In this architecture, a simulation application runs for a number of timesteps previously defined by the user and periodically shares the data that it generates with analytics. This sharing is generally accomplished using a I/O middleware system such as ADIOS [63]. Figure 1.2 shows how these enclave components cooperate within a single node. Note that parallel instances of each workload run on thousands of nodes performing a number of iterations comprised of local computations and barrier syn-

chronization steps. This application model is called *Bulk Synchronous Parallel* [84] because it facilitates the concurrent execution of local computation across processes, and allows parallel progress through the use of synchronization points.

#### Analytics

As the simulation generates data, it is consumed by analytics which uses the I/O middleware to receive that data from the transport channel and then generate useful information for the application scientist. Often, data flows from simulation to analytics; however data may flow from analytics to simulation to guide the computational operations performed by simulation, such in computational steering codes. Among the tasks performed by analytics codes are visualization and steering [88], cosmology analytics [71], data preparation and histogramming [89], and molecular dynamics analysis and visualization [86].

#### 1.1.2 System Support Activities

In order to support applications, a number of operating system tasks run in the background. Those tasks provide the infrastructure services required by applications, but at the same time are a potential source of interference. This section describes those system activities.

#### Short-lived Tasks

The interference generated by background system activities has been widely studied [29,44,66]. Among the system activities that may affect application performance in greater degree are interrupts, scheduling events, and I/O operations [66]. Although these are generally short duration events, their effects can be significant on

applications. Understanding those effects in future systems is important.

#### **Resilience Tasks**

As HPC systems grow in capacity and hardware components, failures will be more common [55, 60]. Those systems will potentially require complex resilience mechanisms to recover from those failures [27,30]. Resilience tasks such as checkpoint/restart will be expensive in future HPC systems and will use a significant percentage of the system available time [67]. This may reduce the time able to be used by applications. Although asynchronous checkpoint/restart, for example, helps to reduce the costs of coordinated checkpoint/restart by relaxing the times in which checkpoints are performed across processes, it is also harmful to applications given the nature of the interference events that it generates.

#### Power Optimization Tasks

Reducing power consumption has been identified as one of the main challenges that future large-scale systems will face [4]. Advances in hardware infrastructure seek to improve energy efficiency; however, they may not suffice without proper system software support [57]. The implementation of these system power management approaches can cause a wide range of problems to HPC scheduling systems. For example, the use of idle power states to save power can generate performance degradation in applications when the sleep length for a core is overestimated [47].

Likewise, Dynamic Voltage and Frequency Scaling (DVFS) techniques influence both BSP application synchronization steps, and complicate scheduling policy decisions. For example, DVFS may affect the duration of individual bulk synchronous intervals generating an effect similar to that produced by OS noise [57]. Similarly, asymmetric DVFS decisions across cores can potentially have large negative perfor-

mance impacts on coordinated scheduling.

### **1.2** The Effects of Interference

As described in Section 1.1, bulk synchronous parallel applications are comprised of iterations in which the parallel components of the applications perform local computations and synchronize at the end of each computation step. The duration of each iteration is dominated by the slowest parallel component, since all parallel components must finish the computation step in order to synchronize. Interference is one of the main factors that influence the interval length.

The effects of interference on parallel applications vary depending on the characteristics of the noise events and the applications' granularity (i.e., the length of the computation iteration [82]) [23]. In the absence of any mitigation mechanism, the individual components of parallel applications may not be affected in the same way; instead they will meet interference events of different duration at different times. This significantly affects communication between components and results in significant performance degradation and variability in the application runtime [21].

Noise events perturbing a given process are *amplified* if they affect the expected end time of a parallel operation, for example increasing the wait time on processes during blocking operations. Other noise events disturbing a process may be *absorbed* if they do not increase the parallel operation's total duration. This may occur, for example, if interfering activities occur while the application is already waiting for other reasons.

Previous work [29] has shown that high-duration low-frequency noise patterns (e.g., analytics codes, resilience tasks) happening during blocking collective operations are more likely to be amplified, while low-duration high-frequency noise events

8

(e.g., short-lived tasks) are more easily absorbed. The application's granularity also influences the noise impact with shorter operations being more sensitive to noise.

#### 1.3 Example

To illustrate these concepts, consider an example based on the Gyrokinetic Toroidal Code (GTC), a code used to study magnetic microturbulence in torus geometries by using a 3D-particle in cell approach to analyze particles interactions [68]. Each particle has a set of features such as position, velocity, and weight [53]. This particle information is shared with PreDatA analytics through an output channel. PreDatA then performs several operations, including global analysis and aggregation of each of the particles' features, range queries to detect particles in a given area, and histogram computations.

As shown in this example, the operations performed both by simulation and analytics codes are complex, as are the interactions between these two workloads. In this example, most of the computational resources are allocated to GTC to perform simulations. Every 5 timesteps, which combined have a duration of approximately 5 seconds, GTC sends data to PreDatA. PreDatA then consumes the simulation data and runs for approximately 100 milliseconds. Both simulation and analytics perform global operations that require communication and synchronization between processes through shared network resources.

In this hypothetical example, both GTC and PreDatA are using one million processes and are time-sharing the same number of CPU cores. While workloads are running, several tasks run in the background in order to facilitate their correct execution. Among these tasks are:

• Short-lived tasks: for example, I/O devices generate interrupts that must be

handled by the corresponding device driver, and the CPU scheduler is executed each time that an interrupt is received.

- Resilience tasks: an asynchronous checkpoint/restart mechanism with checkpointing tasks of one second duration every two minutes like the described in [30] runs in order to protect workloads from system failures.

- Power optimization tasks: a DVFS mechanism attempts to reduce power consumption by independently controlling CPU frequencies.

These sources of interference impact the duration of bulk synchronous intervals and the overall workloads' performance in different ways. The bursty nature of the interference pattern that PreDatA generates in GTC has a potentially high impact on GTC performance. Similarly, the uncoordinated nature of the checkpointing events and their lower-frequency higher-duration pattern may generate even more significant impacts. Since the DVFS mechanism used in this example perform changes in CPU frequencies independently, it will impact the duration of bulk synchronous intervals in different ways, having a potentially high impact on the total workloads' completion time. Finally, short-lived tasks will also contribute to workload performance degradation.

### **1.4** Mitigating Interference Impacts

As described in Sections 1.2 and 1.3, the effects of interference may be important if applications and noise patterns meet certain characteristics. Given their stochastic nature, interference events impact individual bulk synchronous parallel intervals in a non-uniform way, increasing the length of the total interval. The length of this interval depends on the slowest process reaching the synchronization barrier. One of the approaches to mitigate this phenomena is to synchronize the occurrence of

interference events in order to generate homogeneous interference patterns across the application's processes, facilitating the communication between them.

This can be accomplished by using system-based gang scheduling or gang scheduling using synchronizing collectives in the workloads' code. System-based gang scheduling leverages tight system synchronization services to schedule interference events at the same time. On the other hand, synchronizing collectives do not rely on system synchronization services; however, as the MPI 3.0 standard recommends [32], application developers must be careful on relying on the synchronization capabilities provided by MPI collectives. These current mitigation mechanism will not scale efficiently, however, and new approaches may need to be explored [78] for future large-scale systems. This is especially critical for applications with very short intervals, which require tight synchronization [78], and is even more problematic if they are affected by interference sources with low-frequency high-duration patterns.

Approaches based on periodic real-time scheduling [50, 61] have shown benefits similar to these traditional mitigation approaches. Those alternative techniques require less strict system synchronization services and may help to mitigate the impact of emerging workloads in HPC systems. Limited research has been done on the efficacy of these techniques, however.

#### **1.5** Research Challenges

The new trends on computational science codes and the advent of the new interference sources described in previous sections brings new interesting research challenges. Although several empirical studies have been devoted to study the impact of OS interference on applications, there is a need of further research on the impacts of emerging interference sources. Additionally, there is a need of more rigorous analytical tools to perform that research. This will allow to use theoretical foundations to characterize

those new interference sources, to study their impact on emerging applications, and to study alternative mitigation approaches that can be used in future HPC systems.

The following is a summary of the research questions that I attempt to address in this work:

- 1. How will emerging interference sources impact applications' performance in next-generation HPC systems, and what is the effect of using different approaches to schedule co-located workloads?

- 2. What are the synchronization requirements of current performance interference mitigation approaches?

- 3. How can we effectively characterize emerging HPC interference sources?

- 4. How can we effectively model the impact of interference sources and mitigation techniques on applications?

### 1.6 Contributions

My thesis is that fine-grained OS scheduling techniques can be effectively used to support the co-location of HPC applications and emerging workloads in next-generation exascale systems. To evaluate this thesis, I first empirically study current approaches to scheduling co-located workloads. I then develop a model-based approach for studying interference workloads. Finally, I use these techniques to examine the effects of using fine-grained OS scheduling to mitigate performance impacts.

The major contributions of this work are:

• A simulation-based method to evaluating the performance impacts of the colocation of emerging workloads and HPC applications.

- An empirical study of the performance impact of different approaches to scheduling applications and co-located workloads;

- An examination (performed in collaboration with other colleagues) of the synchronization requirements of traditional gang scheduling approaches used to reduce the performance impact on applications;

- An extreme value theory-based approach to modeling traditional and new interference sources, predicting their impact, and informing the design of scheduling techniques to assist in their co-location with HPC applications.

- A validation of the analytical model that I propose, by characterizing several sources of interference and predicting their impacts on a set of applications.

- An evaluation of a fine-grained OS scheduling performance interference mitigation technique using both the empirical and the analytical approaches that I present in this dissertation.

### 1.7 Dissertation Outline

The remainder of this document is organized as follows: Chapter 2 provides essential background information and discusses related work on application composition, performance interference in HPC applications and extreme value theory concepts. Chapter 3 presents a framework that I developed in collaboration with other colleagues. The chapter then uses the framework to quantify the costs and benefits of different approaches to scheduling applications and workloads on nodes in largescale applications, including space sharing, uncoordinated time sharing, and gang scheduled time sharing. Chapter 4 presents an extreme value theory-based model for analyzing the performance of bulk-synchronous HPC applications under the presence of co-located workloads. Chapter 5 evaluates fine-grained OS scheduling policies as

a means to support code co-location both empirically and using the extreme value modeling approach that I propose in this dissertation. Finally, Chapter 6 concludes and presents directions for future work.

# Chapter 2

# **Related Work**

This chapter describes past work related to this dissertation. Section 2.1 presents an overview of the composition of HPC applications as well as the system mechanisms and scheduling techniques required to support it. Section 2.2 describes previous research on the characterization of sources of interference in HPC systems. Section 2.3 studies works on analytical modeling of applications performance and the impact of interference. Section 2.4 provides a study of current interference impact mitigation strategies. Finally, Section 2.5 contrasts the works described here against this dissertation, and explains the novel contributions of my work.

#### 2.1 Application Composition

A major source of interference for next-generation HPC applications are the workloads used for *in situ* data analysis, steering, data aggregation, and visualization that they feed. Such codes are used, for example, to provide new analysis capabilities to existing simulation codes, optimize I/O performance by reducing system I/O demands, and provide summary information at runtime that scientists can use to

Chapter 2. Related Work

monitor the behavior of the simulation.

#### 2.1.1 Example Composite Codes

There are a large number of analytics codes [71,86,88,89]. In this dissertation, I focus on two modern *in situ* analytics workloads, using them to quantify the potential impact of analytics on applications' performance, the *Bonds* analysis used with the LAMMPS application code and a histogramming analysis for the GTC-P proxy application performed using the PreDatA analytics middleware.

SmartPointer Analysis in LAMMPS: SmartPointer [86] is an analytics and visualization code comprised of configurable analytics services. The *Bonds* capability of SmartPointer facilitates the tracking of cracks generated by the LAMMPS simulation code [73]. Specifically, Bonds directly reads atom bonding information from LAMMPS, and conducts a compute-intensive analysis that determines where in a simulated material adjacent molecules are no longer bonded. It then writes the computed information to a previously configured output channel. Bonds performs no additional communication of its own; it relies on communication by LAMMPS to obtain ghost cell information from other nodes.

**PreDatA - Preparatory Data Analytics in GTC-P:** PreDatA is a middleware with pluggable components that perform a number of data preparation operations such as data sorting, filtering, and histogram generation. Those operations are predefined according to the users needs [89], and frequently used so that scientists can monitor the progress (and potential correctness) of long-running simulations. A number of applications have used PreDatA to perform *in-situ* analytics, including the Gyrokinetic Toroidal Code (GTC) [51], a computational-science application used for

#### Chapter 2. Related Work

3D particle-in-cell simulations of plasma micro-turbulence, and Pixie3D [11], a 3D MHD (Magneto Hydro-Dynamics) solver.

#### 2.1.2 System Software Support for Analytics

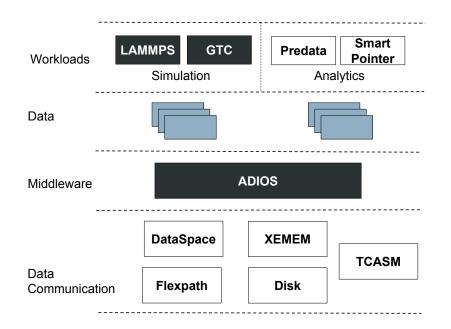

A range of system software techniques have been developed to support *in situ* analytics including, data movement, consistency management, and scheduling techniques. Figure 2.1 shows an example of the stack that simulation and analytics codes use to support their activities. The Adaptable I/O System (ADIOS) [63] provides an API applications can use to efficiently transport data either to other applications or to the file system. It is a flexible middleware that allows applications to choose between different data transport methods at runtime.

There are several alternatives to data transport. The Transparently Consistent Asynchronous Shared Memory (TCASM) [3] API provides low-overhead interfaces for asynchronous memory sharing between codes, while also providing consistent views of shared data using virtual memory techniques. Flexpath [18] uses a public/subscribe mechanism to facilitate data transport between coupled codes by using either shared-memory, Remote Direct Memory Access (RDMA), or TCP/IP communication. Finally, DataSpaces [22] offers data transport and coordination capabilities using RDMA as communication layer.

New HPC system software architectures, for example the Hobbes exascale operating system [9], seek to provide more systematic support for multi-component applications. The Hobbes XEMEM (Cross Enclave Memory) [52] abstraction, for example, provides a shared-memory system between enclaves which is compatible with XPMEM [87]. The Cross-Enclave Asynchronous Shared Memory (XAMS) [24] approach leverages XEMEM and a copy-on-write technique to facilitate application composition by providing an interface to communicate between application compo-

Figure 2.1: System software support for *in situ* analytics

nents using a consumer-producer approach. The coupled codes that I study in this dissertation use ADIOS and XEMEM as middleware and data transport, respectively.

### 2.1.3 Scheduling Analytics

Analytics can be scheduled in a variety of ways, broadly categorized as either spaceshared, where cores are dedicated to analytics, or time-shared, where cores are shared between application and analytics. Space sharing is simpler but requires dedicating resources to analytics, while time-sharing can overlap analytics computation with application computation but directly interfere with application performance.

Time-sharing scheduling approaches include uncoordinated time sharing and gangscheduled time sharing. In uncoordinated time sharing, each node schedules when

analytics runs using a purely local scheduling policy. In gang-scheduled time sharing, a system-wide mechanism coordinates when analytics runs, for example using synchronized clocks, collective communication in the analytics, or collective communication in the application. Methods that avoid introducing extra global communications are generally preferable because of the cost of those communications in large-scale systems.

New services to cooperatively co-schedule analytics and simulation are also under development. The Goldrush system [90], for example, proposes user-level mechanisms to enable simulation/analytics co-location, particularly on OpenMP applications with significant serial execution sections. This work has demonstrated the viability of time-sharing analytics and simulation but relies on significant changes to the application runtime. It is unclear if similar time-sharing approaches are appropriate for a broader range of applications or more general OS-level support could provide similar capabilities.

Chang et al. in [12] propose an approach in which workloads are classified as I/O-intensive or CPU-intensive. They claim that in high speed networks, where the costs of processing huge amount of packets are elevated, I/O-intensive tasks may not receive enough access to CPU resources, which are usually allocated to CPU-intensive tasks. They propose a solution in which CPU-intensive tasks voluntarily yield CPU cycles to I/O-intensive tasks.

### 2.2 Performance Interference

A large number of works have empirically studied the impacts of performance interference. Most have focused on the impact of short-lived background system activities, while a few have studied the effects of other interference sources. Different techniques have been used to these studies, ranging from implementation-based to simulation

and emulation-based approaches. This section describes these approaches.

### 2.2.1 Performance Interference Characterization

OS noise [72] is the most well-known and studied interference source. Some authors [5, 44] have studied the influence of OS noise on BSP applications and the benefits of synchronizing noise events. Pradipta et al. [19] identified the sources of jitter that are potentially more harmful for applications. They found that timer interrupts are the OS noise events that generate the most significant amount of interference, representing approximately a 63% of the total jitter in systems. Further works [29, 66] have investigated the impact of kernel activities on application performance and how system design decisions such as the location of noisy nodes influence performance [28].

Many other sources of interference have also been identified, including asynchronous checkpointing [30, 60], *in situ* analytics systems [90], and system power capping [70]. These sources are particularly interesting because of the increasing importance of application composition and dynamic resource management in nextgeneration HPC systems and applications [9, 53].

### 2.2.2 Summary

Despite all these empirical interference studies, however, the HPC community has only a rough understanding of exactly *how* HPC applications are perturbed. For example, OS noise studies have empirically demonstrated that the "shape" of the noise is at least as important as the amount of noise; infrequent, long-duration noise events have been shown to be significantly more disruptive than frequent shortduration noise events [29, 41].

These studies are almost exclusively empirical with little or no theoretical or analytical underpinning to help researchers understand *why* interference interacted with applications in the way it did or provide quantitative predictions about how particular interference sources and applications would interact. In contrast, this dissertation seeks to provide the theoretical foundations to characterize interference sources, predict their impact on applications and understand performance interference mitigation strategies.

### 2.2.3 Simulating Interference Performance Impact

Several researchers have used simulation and emulation techniques in order to investigate the potential effects of interference on applications running on future largescale systems. This facilitates study of those impacts using scales and capabilities not present in current systems. A number of works, including that described in this dissertation have used LogGOPSim. In the remainder of this section, I describe LogGOPSim in detail, as well as information on other simulation approaches.

#### LogGOPSim Extreme-scale Simulator

LogGOPSim [42] has been used to investigate the effects of noise and noise-like phenomena on application performance. Hoefler et al. [41] used this simulator to evaluate the effects of OS noise on application performance. Levy et al. [60] demonstrated that LogGOPSim could be used to accurately predict the impact of resilience mechanisms on applications performance. Ferriera et al. [30] subsequently used LogGOPSim to consider the impact of asynchronous checkpoint/restart on application performance. Widener et al. [85] used LogGOPSim to study how non-blocking collectives might be used to reduce the performance penalties associated with asynchronous checkpoint/restart.

LogGOPSim uses the LogGOPS model based on LogP [16]. It simulates traces collected from small applications runs, reproducing messages between processes and communication dependencies [30]. It also provides an extrapolation capability which performs simulations at larger scales [42]. LogGOPSim simulates the impact of noise by reading a noise trace. This noise trace contains noise events, characterized by their starting time and duration, which are added to the communication or computation events during simulation.

LogGOPSim provides the capability to simulate the level of synchronization of interference events by controlling the point in which each process starts reading the noise trace. If the starting points across processes are selected uniformly at random, LogGOPSim simulates total uncoordinated scheduling of noise events. If the starting points are selected from a normal distribution, it simulates gang scheduling with different levels of synchronization. The degree of coordination is controlled with the standard deviation of the distribution.

#### Other Simulation Approaches

Other works have used simulation and emulation approaches. Engelmann et al. [23] use the extreme scale simulator (xSim) [8] to investigate noise impacts on HPC systems with up to 2M nodes and 1 billion cores. They study the effects of noise amplification and noise absorption on MPI collectives and propose this framework as a tool to be used in hardware/software co-design of future HPC systems. Pradipta De et al. [20] propose an emulation-based approach to study the impact of noise and the mitigation effects of jitter synchronization. Unlike LogGOPSim, which provides the capability of performing large scale analysis running simulations in a single node, these frameworks require large amounts of systems resources which increase with size of the extrapolation under analysis.

In this dissertation, I leverage LogGOPSim to study the impact of new sources of interference on HPC applications. I also use it to collect the baseline application's data that feed my performance interference analytical model.

### 2.3 Modeling Performance Impact

A few works have used mathematical-based modeling to study application performance interference. A number of works leverage probabilistic and statistics of extremes concepts to provide the theoretical foundations to understand this problem. This section describes these works and introduce the theoretical foundations that they use.

### 2.3.1 Modeling Extremes

Extreme Value Theory (EVT) and the Expectation of Maximum Values (EMV) concepts have been widely used across a variety of domains to estimate the probability of extreme events. These theories have been recently used in computer science to estimate applications' performance [81] and the impact of jitter [78]. I next discuss these and additional related works.

### Extreme Value Theory

Extreme Value theory (EVT) is a sub-field of statistics focused on the behavior of maxima of a set of random variables [43]. It is generally used to analyze or predict the likelihood of extreme events occurring. EVT works with a set of independent, identically distributed (i.i.d.) stochastic events of potentially unknown distribution, and seeks to understand when a new extreme value (a sample larger than those seen

previously) should be expected to happen.

EVT has been used in fields such as hydrology to determine long-term flood plain levels, and for similar actuarial analyses in the insurance and financial industries. It has also been used to estimate the size of demand bursts in internet traffic [37]. Similarly, Uchida et al. [83] present a model that uses extreme value theory to explain the tail of the distribution of throughput and as a tool to predict peaks of throughput.

EVT methods generally focus on the use of the Generalized Extreme Value (GEV) distribution. This distribution combines different related distributions in which the maximum value of a set of independent and identically distributed random variables can be fitted assuming distributions with well-behaved tails.

$$F(x \mid \xi, \mu, \sigma) = e^{-\left[1 + \xi\left(\frac{x-\mu}{\sigma}\right)\right]^{\frac{-1}{\xi}}}$$

(2.1)

Where,

$$-\infty < \xi < \infty$$

,  $-\infty < \mu < \infty$ , and  $\sigma > 0$

Equation 2.1 shows the cumulative distribution function (CDF) for the GEV distribution, which includes three parameters, shape ( $\xi$ ), location ( $\mu$ ) and scale ( $\sigma$ ). The *location* parameter determines the shift of the distribution to left or right direction. The *scale* parameter defines the dispersion of the distribution; the greater this parameter the greater the dispersion. A property of the scale parameter is that if it is multiplied by a constant, c, the random variable will be multiplied as well. Thus, for a random variable X,  $|c| \times \sigma(X) = \sigma(c \times X)$  [76]. The *shape* parameter defines if the distribution of maxima belongs to the lightly-tailed *Gumbel* ( $\xi = 0$ ) distribution, the heavy-tailed *Fréchet* distribution ( $\xi > 0$ ), or the upper bounded-tail *Weibull* distribution ( $\xi < 0$ ).

The *block maxima method* from EVT is a commonly-used technique for fitting the GEV distribution to the maximum of a set of random samples of a random variable. In this method, the observations of a given random variable are divided into blocks of

size n and the maximum value occurrence in each block is determined. A traditional distribution fitting method, commonly maximum likelihood estimation (MLE), is then used to determine the GEV parameters that best fit this set of maxima. The resulting distribution is that of the maxima of blocks of size n. In flood plain analysis, for example, the block maxima method is frequently used with blocks of 365 days to estimate GEV parameters for the distribution of maximum annual water levels.

The regularity of the maximum likelihood estimators and the degree in which they meet the asymptotic property of a GEV distribution can be established by studying the  $\xi$  parameter [14,79]. For  $\xi$  parameters greater than -0.5, regular likelihood estimators can be obtained. For  $\xi$  parameters between -1 and -0.5 likelihood estimators can be obtained but they do not meet the asymptotic property of a GEV distribution. Finally, for  $\xi$  parameters less than -1, is generally not possible to compute the estimators.

Given a concrete GEV, return level analysis can then be used to compute the return level,  $\bar{R}$ . This return level can be interpreted as the value that will, on average, be exceeded once in every N samples of the distribution. Note, that this is once every b blocks when using the block maxima method to fit the GEV distribution. In the common flood plain level, for example, the 100-year flood plain is simply the 100-year return level once the GEV parameters for the distribution of annual maximum waters levels have been determined. Details of this calculation have been omitted for brevity and are available in the literature [14].

#### **Expectation of Maximum Values**

In addition to return level analysis, extreme value techniques also sometimes seek to directly calculate the expected value of the maximum of a set of random variables, an area termed *expectation of maximum values* (EMV). A number of approximation

techniques have been proposed for this problem [7, 25, 31, 35, 81].

Modeling Application Runtime Recent work [81] used the expected mean maximum approach (EMMA) to estimate execution times in BSP applications when the probability distribution of process local computation times is known *a priori*. In particular, this technique estimates the expected value of the maximum m instances of a set of i.i.d. random variables  $X_i$  with distribution F as:

$$E(max_{i=1}^{m}X_{i}) \approx F^{-1}(P) \tag{2.2}$$

where  $P \approx 0.570376002^{1/m}$ .

This dissertation provides a novel approach that uses EVT concepts to characterize interference sources and study their impact on applications. While EMMA [81] used extreme value concepts to derive the expected mean maximum approximation, it did not use extreme value distributions themselves to estimate application performance. This limits EMMA's direct use in application performance estimation. However, the method described in this work for conducting such estimations relies heavily on EMMA for extrapolation. EMMA focuses on runtime estimations for applications running in isolation. Unlike EMMA, our model focuses on the impact of interference in time-shared environments, and does not assume similar computation efforts across BSP iterations.

**Modeling Interference** Seelam et al. [78] use expectation of maximum values analysis to predict the effects of jitter on applications. To that end they use a simple synthetic Bulk Synchronous Parallel (BSP) benchmark to study the effect of short-lived noise events for BSP computational intervals of different lengths. They compute lower and upper bounds of the expected slowdowns using the approxima-

tions proposed by Bertsimas [6] and Crammer [15], respectively. They then use the data provided by the benchmark's runs to estimate the probabilistic parameters used by those models and estimate slowdowns at larger scales. By using their model, they state that the slowdown experienced by an application is proportional to  $\sqrt{n}$ , where n is the number of CPUs in the system. They also use the model to study the mitigation effects of co-scheduling.

The Bertsimas and Cramer bounds used by Seelam et al. [78] roughly estimate the impacts of OS noise; however the exact distribution of the noise is not computed. This is reasonable to estimate the modest impacts of OS noise but not sufficient to estimate the impacts of more extreme types of interference. The model that I propose in this dissertation, in contrast, estimates the underlying distribution of BSP computational intervals under the effects of a variety of noise types. Moreover, Seelam et al. leverages the synthetic benchmark for all experiments. This may suffice for well-balanced real applications in co-location with modest interference. However other approaches are needed to study interference sources such as analytics codes or resilience operations.

### 2.3.2 Other Analytical Models

Tsafrir et. al. [82] used probabilistic methods to demonstrate the linear dependency of applications' performance interference and the size of a system. They propose a simple model that states that given a system of n nodes, if the per-node probability of an application being delayed is p and  $p \leq \frac{1}{10n}$ , the noise affecting the parallel application on each computational iteration is directly proportional to the system size with a probability of the application being delayed given by  $p \times n$ . The pprobability is measured by benchmarking the application to estimate the probability distribution of computational iterations. This model provides a general sense of the

probability of application delays, but it can not be used to compute the expected application slowdown. The model that I propose in this dissertation seeks to estimate the expected application slowdown.

### 2.4 Performance Impact Mitigation

Many techniques have been proposed for mitigating the impact of performance interference on HPC applications. A number of works have used gang scheduling-based techniques to minimize the impact of potentially interfering workloads. Other works have propose alternative approaches based on periodic real time scheduling. This section describes those works.

### 2.4.1 Gang Scheduling

Using gang scheduling has shown performance benefits for BSP applications. When using this technique, the application's processes are co-scheduled. This facilitates the communication between them and reduces the amount of time that the fastest processes have to wait for synchronization.

Feitelson et al. [26] in one of the first works that studied gang scheduling, compared two synchronization techniques: (1) a busy waiting-based gang scheduling technique implemented by the runtime which schedules application processes at the same time; and (2) a blocking, with uncoordinated scheduling, synchronization mechanism. They show that fine-grained parallel applications benefit from using the gang scheduling policy, which otherwise incur overheads due to context switching while blocking to perform synchronization.

More recently, Jones et al. in [44] presented a run-time system to avoid the inter-

ference over large fine-grained parallel applications generated by short-lived system tasks. This run-time coordinates those system tasks in order to run them at the same time. This helps to decrease interference impacts, allowing parallel applications to be co-scheduled at precise times, and improving their performance and scalability. This approach works for both inter-node and intra-node cases. In this dissertation, we use simulation to study the global synchronization requirements of traditional gang scheduling-based mitigation approaches.

### 2.4.2 Real Time Scheduling Mitigation

Local scheduling policies are generally the purview of the operating and application runtime systems. In best-effort scheduling, typified by Linux's round-robin preemptive priority scheduler, the CPU is shared roughly equally when both analytics and the application need to run. Earliest-deadline-first (EDF) scheduling, in contrast, provides fine-grain control of when each task runs and the share of the processor given to each task, and has been proposed to mitigate performance interference.

### Earliest Deadline First (EDF) Scheduling

Earliest Deadline First (EDF) is a periodic real time scheduling algorithm. An EDF scheduler uses a dynamically calculated priority value as the scheduling criterion to choose what task will be scheduled. This priority value is calculated according with the relative deadline of the tasks that are ready to run in a *runqueue*. The tasks with less time before their deadline will receive higher priorities. At each opportunity to make a scheduling decision (e.g., when an interrupt is received), the scheduler executes the task that has the deadline that will expire first.

Each task's scheduling requirements in EDF scheduling are described by a scheduling *period*, T, and the length of the task's *slice*, S, within that period. A task with

a slice S and a period T is guaranteed to execute for S seconds in each T second period. Usually, the deadline for each task is assumed to be the expiration of its current period.

A task uses at least slice (S) seconds of CPU every period (T). The period is defined as the time in which the task may receive a CPU allocation, and the slice is the minimum amount of time received for the task during each period [62]. The portion of the CPU used for a task i (i.e., *task's utilization factor*) is

$$u_i = \frac{S_i}{T_i} \tag{2.3}$$

and the processor's utilization is given by:

$$U = \sum_{i=1}^{n} \frac{S_i}{T_i} \tag{2.4}$$

Where n is the number of EDF tasks running on that processor.

The schedulability condition [62] is given by,

$$\sum_{i=1}^{n} \frac{S_i}{T_i} \le 1 \tag{2.5}$$

This schedulability condition guarantees that no task will miss deadlines if the CPU utilization is at most 100%.

### **EDF-Based** Mitigation

An alternative performance interference mitigation technique leverages the EDF scheduling policy. In this approach, applications processes are co-scheduled in differ-

ent system partitions and configured with identical EDF parameters. This approach can be used, for example, to reschedule analytics workloads time-sharing CPU cores with simulation, resulting in frequent, limited-duration interruptions of the simulation application.

Bin Lin et al. [61] present an approach based on per-node EDF schedulers. This technique provides mitigation capabilities comparable to those offered by gang scheduling by setting the same slice and period values to all of the application's parallel components. This approach schedules virtual cores to the same host CPU cores and leverages the synchronization and isolation capabilities of EDF to mitigate the effects of contention and keep the virtual machines' computation rate constant. In this dissertation, I use this approach to study the performance interference mitigation effects of using periodic real scheduling to schedule co-located workloads.